復旦大學《集成電路設計導論》第3節 設計驗證教程、筆記、習題及代碼資源綜合指南

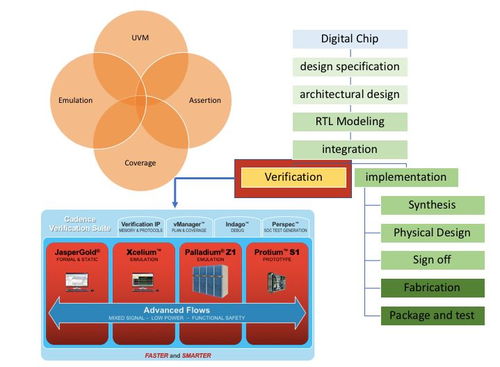

設計驗證是集成電路(IC)設計流程中的關鍵環節,它確保設計在功能、時序和物理層面符合規格要求,是保證芯片正確性與可靠性的基石。本節將系統講解設計驗證的核心概念、方法、工具鏈,并提供相關的學習資源與實戰指南。

一、 設計驗證概述

1. 驗證的重要性

在納米級工藝時代,芯片復雜度呈指數增長,一次流片(Tape-out)失敗的成本極其高昂(可達數百萬甚至上千萬美元)。設計驗證的目的就是在芯片制造前,盡最大可能發現并修正所有設計錯誤。據統計,驗證工作通常占據整個設計周期的60%-70%。

2. 驗證層級與流程

驗證是一個多層次、漸進的過程:

- 模塊級驗證:針對單個功能模塊(如ALU、FIFO)進行測試。

- 子系統/芯片級驗證:驗證多個模塊集成后的功能。

- 系統級驗證:將芯片置于虛擬或真實的系統環境中進行驗證。

- 物理驗證:包括DRC(設計規則檢查)、LVS(版圖與電路圖一致性檢查)、ERC(電氣規則檢查)等。

主要流程包括:制定驗證計劃、搭建測試平臺(Testbench)、編寫測試用例(Testcase)、執行仿真、分析結果并覆蓋率(Coverage)評估。

二、 主要驗證方法學

1. 動態仿真(Simulation)

- 數字仿真:使用EDA工具(如VCS, NC-Verilog, ModelSim)在軟件環境中模擬電路行為。測試平臺通常用SystemVerilog或UVM(通用驗證方法學)搭建。

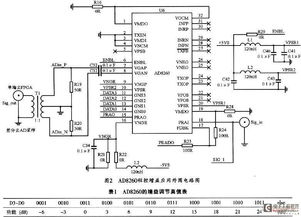

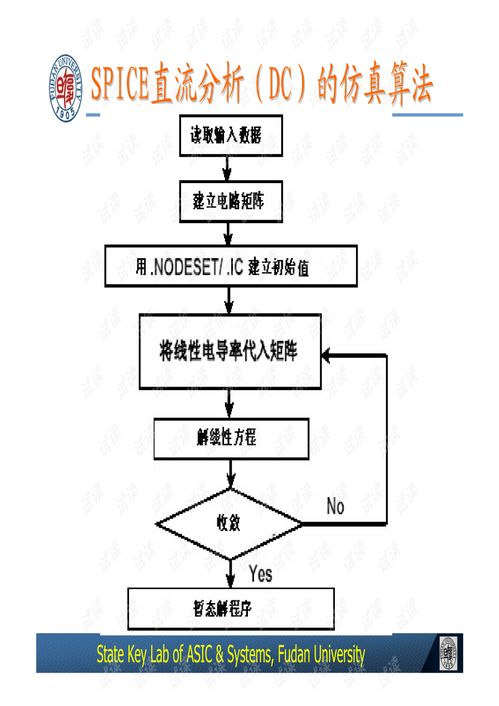

- 模擬/混合信號仿真:使用SPICE、Spectre等工具進行晶體管級仿真,精度高但速度慢。

2. 靜態驗證(Static Checking)

- 形式驗證(Formal Verification):使用數學方法“證明”設計在某些屬性上是否正確,無需測試向量。適用于控制密集型模塊。

- 靜態時序分析(STA):在提取寄生參數后,對設計進行全面的時序檢查,確保在所有角落(Corner)下都滿足時序要求。

- 等價性檢查(LEC):驗證綜合后網表或修改后網表與原始RTL功能是否等價。

3. 硬件加速與原型驗證

- 硬件仿真(Emulation):使用FPGA陣列或專用硬件仿真器,速度比軟件仿真快數個數量級,適合系統級驗證。

- FPGA原型驗證:將設計移植到FPGA上進行實速驗證,便于早期軟件開發與系統集成。

三、 驗證語言與平臺搭建

1. 主流語言

- SystemVerilog:當前數字驗證的事實標準,集成了面向對象、約束隨機、斷言等高級特性。

- UVM:基于SystemVerilog的類庫和方法學,提供了可重用、標準化的驗證平臺框架。

- Python/Perl/Tcl:廣泛用于編寫驗證腳本、結果分析和流程自動化。

2. 測試平臺基本組件

一個典型的UVM測試平臺包含:

- Test:頂層測試類,用于配置環境并啟動測試。

- Environment:包含多個可重用的組件。

- Agent:包含驅動器(Driver)、監視器(Monitor)和序列器(Sequencer),負責接口級的激勵生成與監測。

- Scoreboard:用于檢查設計輸出是否正確(參考模型比對)。

- Coverage Collector:收集功能覆蓋率和代碼覆蓋率。

四、 教程、筆記與習題實戰指南

1. 理論學習要點

- 深入理解驗證計劃、測試用例、斷言、覆蓋率的定義與制定方法。

- 掌握SystemVerilog的關鍵特性:類、隨機化、約束、接口、斷言(SVA)。

- 理解UVM的相位機制、配置機制、工廠模式及消息服務。

2. 習題與項目實踐

- 基礎習題:針對簡單模塊(如計數器、狀態機)編寫直接測試向量和SystemVerilog斷言。

- 進階項目:為一個稍復雜的IP(如UART、SPI控制器或AXI互聯模塊)搭建完整的UVM驗證環境。要求包括:

- 編寫驗證計劃。

- 搭建分層測試平臺。

- 實現約束隨機測試。

- 集成功能覆蓋與代碼覆蓋。

- 編寫回歸測試腳本。

五、 代碼類資源與獲取建議

關于CSDN等平臺的資源下載提示:

在CSDN、GitHub、OpenCores等平臺,可以找到豐富的學習資源,包括:

- 參考代碼:UVM驗證平臺模板、常見接口(APB, AHB, AXI)的驗證組件、典型IP的驗證環境。

- 項目實例:從簡單到完整的小型SoC驗證示例。

- 腳本工具:用于覆蓋率合并、回歸測試管理的Perl/Python腳本。

使用建議與注意事項:

1. 甄別質量:下載代碼時,注意查看上傳者信譽、代碼更新日期和用戶評價,優先選擇結構清晰、注釋完整的項目。

2. 理解而非復制:核心目標是學習代碼結構和設計模式。務必逐行理解,并嘗試修改、擴展功能。

3. 知識產權:注意資源的開源協議(如Apache, MIT),尊重原作者版權,謹慎用于商業項目。

4. 結合官方文檔:最權威的資料永遠是EDA廠商(Synopsys, Cadence, Siemens EDA)的官方工具手冊和UVM官方標準文檔。

六、

設計驗證是一門理論與實踐緊密結合的工程學科。掌握它需要:

- 堅實的理論基礎:理解驗證方法學與流程。

- 熟練的工具使用:掌握主流仿真、調試、覆蓋率分析工具。

- 大量的編碼實踐:通過閱讀優秀代碼和親手搭建驗證平臺來積累經驗。

- 系統性的思維:從制定計劃到覆蓋率閉環,具備完整的項目把控能力。

建議學習者以一個小型但完整的設計驗證項目為主線,將本節所述的理論、方法和資源貫穿起來,在實踐中不斷深化理解,從而真正掌握集成電路設計驗證這項至關重要的技能。

如若轉載,請注明出處:http://www.dweilong.cn/product/84.html

更新時間:2026-04-28 00:40:13